Sự ra đời của chiplets • Bài viết • Niềm say mê, bộ dụng cụ thiết kế chiplet cho tích hợp không đồng nhất 3D IC | Phần mềm Siemens

Sử dụng bộ dụng cụ thiết kế Chiplet để giúp mở đường cho tích hợp không đồng nhất IC 3D

Vài năm sau, các bộ xử lý đầu tiên xuất hiện với Intel 4004 đặc biệt. Sau đó, các bộ xử lý trở nên phức tạp hơn.

Sự ra đời của Chiplets

Sau một cuộc thảo luận về JZDS và về sự bất hòa, tôi đã nói với bản thân mình rằng viết một bài báo trên các chiplets sẽ có lợi cho số lượng lớn nhất. Và sẽ giữ một bản nhạc bằng văn bản trái với những gì có thể xảy ra với JZDS

Thay vì viết một vé rất dài, tôi thích định dạng của bài viết hơn một chút về các chi tiết. Tôi hy vọng có thể dạy cho bạn những con chiplets là gì, tại sao công nghệ này được tạo ra và tại sao nó sẽ phát triển trong những năm tới.

- Lời mở đầu

- Chiplet, Quésaco ?

- Các khía cạnh kinh tế của Chiplets

- Hai ví dụ: AMD và Intel (Altera)

Lời mở đầu

Bài viết này nói về các khái niệm máy tính, điện tử và kiến trúc của các máy tính có thể đủ nâng cao cho một số độc giả nhất định. Tôi cung cấp cho bạn một chút phổ biến trong phần mở đầu này để hiểu tốt hơn một chút những gì chúng ta đang nói về.

Đối với những người theo chủ nghĩa thuần túy, các phím tắt sẽ được thực hiện, sự phổ biến này có thể chứa thông tin tự nguyện không chính xác để tạo điều kiện cho sự hiểu biết.

Chiplet, Quésaco ?

Hãy bắt đầu với khó khăn nhất, xác định con chip là gì !

Thật vậy, thuật ngữ Chiplet xuất hiện vào những năm 1970 nhưng việc sử dụng nó chủ yếu đã bị loại bỏ trong những năm gần đây, đối với những người quan tâm đến bộ xử lý phức tạp hoặc chip điện tử như FPGA (chip có cửa logic bên trong có thể được lập trình lại). Đối với những người khác, ở dưới cùng của căn phòng, bạn có thể chưa bao giờ nghe về thuật ngữ này, chúng tôi sẽ khắc phục nó !

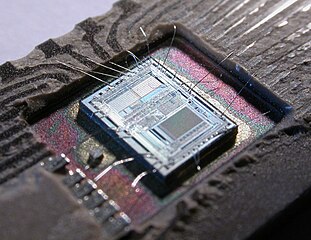

Hãy quay trở lại cơ sở của một con chip điện tử là gì: một mảnh silicon khắc (bóng bán dẫn nổi tiếng) được gói gọn trong một trường hợp. Với các thành phần giao nhau, các sợi vàng hoặc bạc nhỏ kết nối chân của thành phần với mảnh silicon. Lúc đầu, các chip được tạo thành từ các bóng bán dẫn được khắc các độ phân giải khá thô (so với ngày nay) và các chức năng khá cơ bản: cửa logic, bộ khuếch đại hoạt động, v.v. Tuy nhiên, đó đã là những tiến bộ to lớn về mặt thu nhỏ !

Vào thời điểm đó, các thành phần có chân chéo và cần phải kết nối chip silicon với các chân này. Nó được làm bằng những người con trai bạc hoặc vàng mỏng được hàn giữa chip và chân bên trong vỏ.

Vài năm sau, các bộ xử lý đầu tiên xuất hiện với Intel 4004 đặc biệt. Sau đó, các bộ xử lý trở nên phức tạp hơn.

Từ những năm 1970, IBM đã phát triển các thành phần MCM (Đa chodu) bao gồm một số chip silicon trong một trường hợp. Nhưng công nghệ này sẽ chủ yếu phát triển vào cuối những năm 90. Chúng ta có thể lưu ý Pentium Pro của Intel được phát hành năm 1995. Bộ xử lý này bao gồm hai chip silicon: một cho bộ xử lý nói một cách nghiêm ngặt và một cho bộ nhớ bộ nhớ cache L2 (bộ nhớ bộ đệm giữa bộ xử lý và RAM, nhanh hơn nhiều nhưng đắt hơn nhiều vì được khắc bằng bộ xử lý).

Như chúng ta có thể thấy trong ảnh, hai chip có cùng kích thước và Intel cung cấp một số kích thước của bộ đệm L2. Ưu điểm của việc phân tách bộ xử lý bộ nhớ bộ đệm là có thể lưu tỷ lệ trên chip bộ xử lý trong khi cung cấp các kích thước bộ nhớ cache khác nhau bằng cách đặt một chip kích thước khác trong trường hợp.

Loại thành phần này vẫn còn kém phát triển, ngay cả khi IBM tiếp tục phát triển các thành phần MCM. Lưu ý Power5 của IBM được phát hành vào năm 2004, nhìn thấy bốn bộ xử lý thẳng đứng với chip bộ nhớ bộ nhớ cache L3. Sự kết nối của bọ chét được thực hiện bên trong trường hợp.

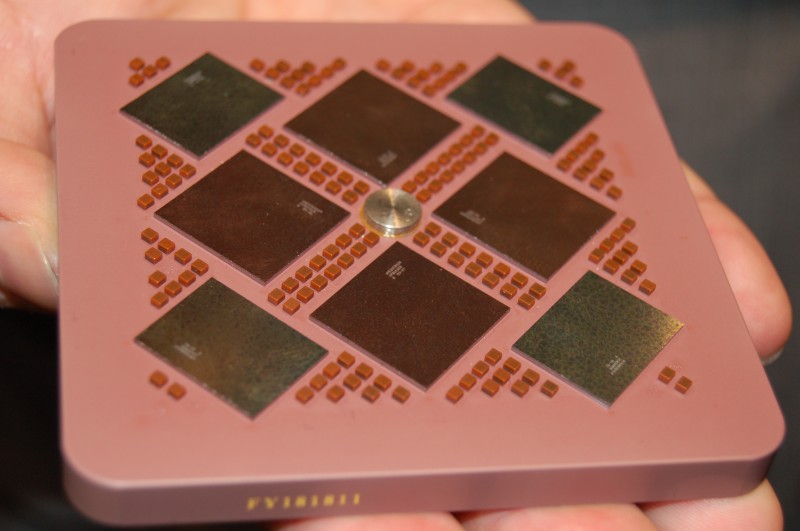

Ngày nay, công nghệ đã phát triển và các chip MCM có mặt trong các sản phẩm tiêu dùng với bộ xử lý AMD. Ở đây chúng ta có thể thấy bộ xử lý EPYC 7702 (được phát hành vào tháng 8 năm 2019) bao gồm 9 chip silicon liên kết: 8 chip chứa lõi và bộ nhớ bộ nhớ cache và chip trung tâm kết nối 8 người khác và quản lý DDR cũng như lối vào tín hiệu/ lối vào/ lối vào/ Thoát (SATA, PCI Express, USB, v.v.)).

Nhưng hãy nói với tôi Jamy, Chiplet là gì ?

À đúng rồi, tôi bắt nguồn một chút

Trên thực tế, một con chip là một trong những chip silicon có trong MCM. Một con chip được tạo ra để được kết nối với nhau với các chiplets khác. Vâng, nó tương đối đơn giản nhưng bạn phải hiển thị một số bức ảnh đẹp để hiểu

Tuy nhiên, chính xác hơn một chút về ý nghĩa của các chiplets, ý tưởng không nhất thiết phải đặt một số chip khác nhau được liên kết với nhau. Ngoài ra còn có một khái niệm về chip chung có thể được sử dụng lại và không dành riêng cho một tài liệu tham khảo bộ xử lý cụ thể.

Các khía cạnh kinh tế của Chiplets

Sau phần giới thiệu này trong khi hình ảnh, bây giờ chúng ta hãy hiểu lý do tại sao các chiplets sẽ phát triển trong tương lai. Để làm điều này, cần phải trở lại quy trình sản xuất bọ chét điện tử.

Ngồi thoải mái trên ghế bành vì chuyến đi từ bãi cát sẽ dài

Không chờ đợi !

Chúng tôi sẽ dành cả một phần của việc sản xuất silicon. Những gì chúng ta quan tâm là sự phân phối của bọ chét (chết) trên bánh silicon (wafer) và đặc biệt là sự tiến hóa của năng suất với sự gia tăng sự tinh tế.

Nhưng trước khía cạnh này của sản lượng, chúng ta phải nói về kích thước vật lý tối đa của một cái chết. Thật vậy, trên một chiếc bánh kếp silicon, cùng một thiết kế của một con chip được lặp lại nhiều lần (hàng chục hoặc thậm chí hàng trăm lần). Ấn tượng của thiết kế này được thực hiện bằng quang học thông qua ánh sáng cực tím. Tuy nhiên, có cả một bộ ống kính và cơ chế quang học ngăn chặn việc khắc một cái chết trên toàn bộ bánh silicon.

Chúng ta càng làm phức tạp bọ chét, chúng ta càng muốn đặt bóng bán dẫn, vì vậy chúng ta phải tăng kích thước của chip hoặc tăng sự tinh tế của việc khắc để phù hợp với nhiều bóng bán dẫn hơn trong cùng một bề mặt. Nhưng quá ràng buộc và giới hạn khác được cảm nhận.

Đây là lý do tại sao nguyên tắc của Chiplet rất thú vị để bỏ qua các giới hạn này: sử dụng một số chip silicum nhỏ được kết nối với nhau để tạo ra một con chip phức tạp hơn nhưng không thể khắc theo cách nguyên khối.

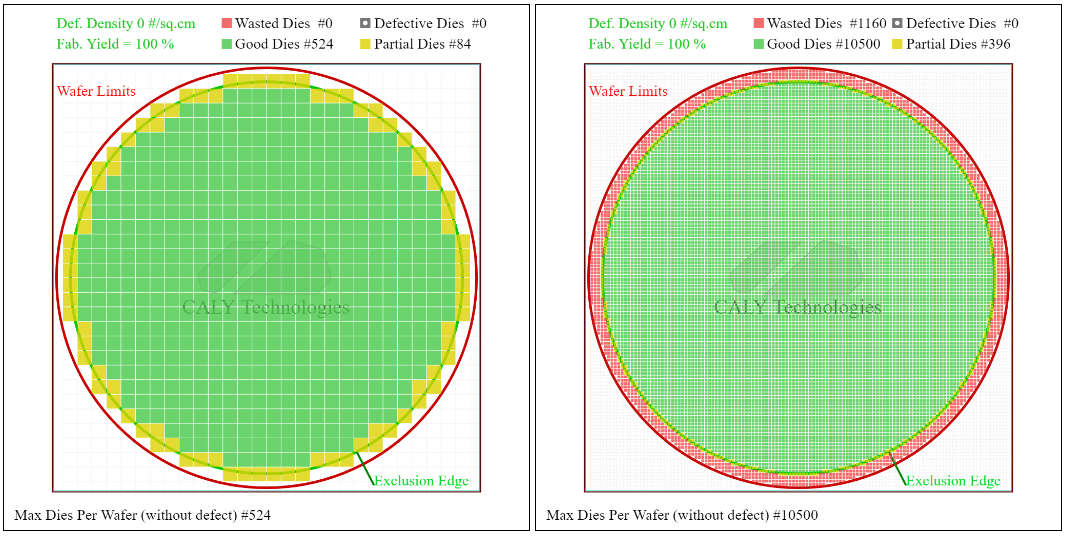

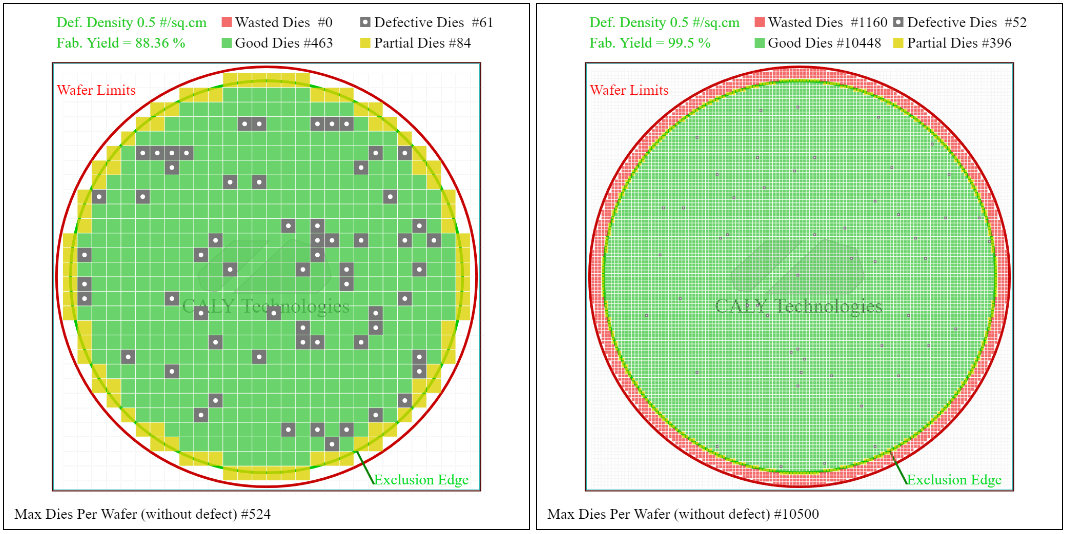

Bây giờ trở lại sản lượng (năng suất bằng tiếng Anh). Đầu tiên, các tấm vải có hình tròn và chúng tôi muốn khắc nó bằng các chip hình chữ nhật. Toàn bộ silicon không được sử dụng. Nhưng những cái chết ở các cạnh càng nhỏ và chúng ta càng có thể có toàn bộ cái chết. Đó là nguyên tắc tương tự như bí danh trong một trò chơi video: càng nhiều pixel được sử dụng để tạo thành hình tròn là nhỏ và chúng ta càng ít nhận ra biệt danh.

Trong ví dụ trên, nếu chúng ta báo cáo một phần chết trên tổng số chết (tốt và sai lệch), chúng ta sẽ có tỷ lệ 13.8 % trong trường hợp chết 5 × 5 mm và 3.6 % trong trường hợp 1 × 1 mm chết. Cái chết càng nhỏ, các cái chết hợp lệ hơn có thể có ở các cạnh, làm tăng năng suất.

Bạn cũng có thể tạo ra một hỗn hợp chết lớn ở trung tâm của wafer và sử dụng các cái chết nhỏ hơn ở các cạnh để tối ưu hóa năng suất do răng cưa.

Nói jamy, tại sao chúng ta sử dụng các tấm vải tròn để làm bọ chét hình chữ nhật ?

Vâng, đó là vì phương pháp tạo ra quy trình silicon được gọi là czochralski cung cấp silicon dưới dạng xi lanh, cắt thành những lát vệt.

Thứ hai, sản lượng bị ảnh hưởng bởi các khiếm khuyết có thể xuất hiện trên wafer. Bạn có thể nghĩ về các hạt bụi rơi trên wafer.

Tôi đã tiếp tục ví dụ trước bằng cách thêm mật độ lỗi là 0.5 mỗi cm². Bây giờ so sánh Sản xuất năng suất tương ứng với tỷ lệ giữa số lượng chết chức năng và tổng số sản phẩm được sản xuất. Trong trường hợp chết 5 × 5 mm, sản lượng là 88.4 % trong khi có chết 1 × 1 mm, sản lượng là 99.5 %.

Do đó, thật thú vị khi có những cái chết nhỏ để tối ưu hóa việc sản xuất bọ chét điện tử. Tuy nhiên, việc cắt một con chip phức tạp thành một số chip nhỏ hơn đòi hỏi phải truyền đạt các chip khác nhau giữa chúng, do đó chúng ta phải thêm các yếu tố giao tiếp đến để chiếm thêm không gian và sử dụng năng lượng bổ sung.

Ngoài ra, việc sử dụng chiplets có thể cho phép sử dụng những cái chết của sự tinh tế khác nhau theo các chức năng cho phép điều chỉnh chi phí của chip cuối cùng với hiệu suất.

Cuối cùng, một khía cạnh kinh tế khác để xem là sự phức tạp của việc phát triển các tính năng mới. Điều này có xu hướng có các công ty chuyên ngành (hoặc ít nhất là khởi nghiệp khi bắt đầu) cung cấp các khối sở hữu trí tuệ (chức năng) sẵn sàng sử dụng. Ví dụ, nhà sản xuất bộ xử lý sẽ có thể tập trung vào việc phát triển chính bộ xử lý trong khi mua chết cho các chức năng như bộ điều khiển PCI Express, USB hoặc DDR.

Để tạo điều kiện cho khả năng tương tác của chiplets đến từ các nhà sản xuất khác nhau, những người chơi chính như Intel, AMD, ARM, Qualcomm, Samsung hoặc TSMC đã tạo ra một tiêu chuẩn giao tiếp giữa Chipplets, UCIE (UCIE (Universal Chiplet Connection Express)).

Hai ví dụ: AMD và Intel (Altera)

AMD EPYC

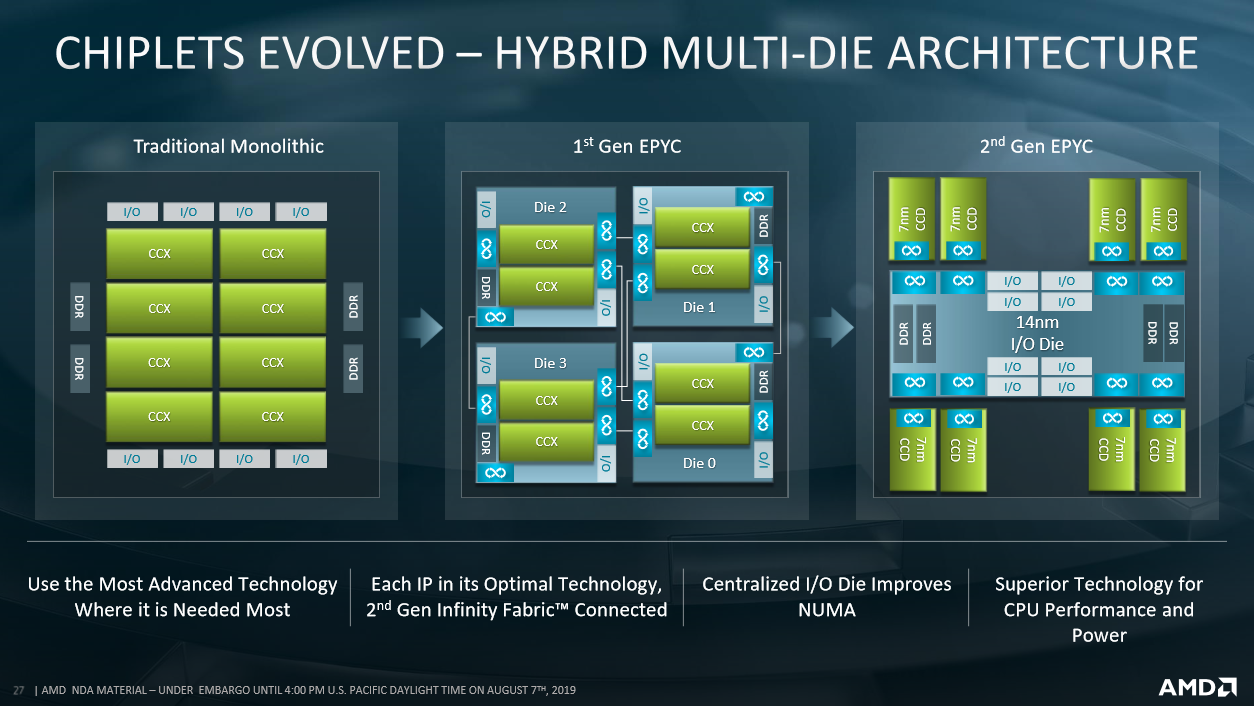

Ngày nay, ngày càng có nhiều bộ xử lý sử dụng kỹ thuật Chiplets này. AMD sử dụng chiplets kể từ thế hệ đầu tiên của bộ xử lý EPYC, trong đó các trái tim khác nhau được liên kết với nhau bởiVải vô cực.

Thế hệ đầu tiên của bộ xử lý EPYC đã thấy một bộ chết có thể được đánh đồng với các bộ xử lý hoàn chỉnh được liên kết với nhau bởiVải vô cực Để tạo ra bộ xử lý cuối cùng. Do đó, các chiplets là một loại bộ xử lý tự trị nhỏ: mỗi cái chết đều quản lý các mục/đầu ra của nó và có bộ điều khiển DDR của nó.

Những cái chết này, hay đúng hơn là Chiplets, có hai Tính toán lõi phức tạp Vải vô cực.

Sự tinh tế nhỏ, luôn có bốn chiplets trên EPYC thế hệ đầu tiên. Để thay đổi số lượng trái tim, AMD vô hiệu hóa trái tim bên trong CCX. Ví dụ: có 24 lõi, CCX chỉ có 3 lõi hoạt động

Do đó, thế hệ đầu tiên này đã sử dụng nguyên tắc chiplets như một loại bản sao/dán của chết thay vì phát triển một cái chết nguyên khối lớn.

Đối với thế hệ thứ hai, AMD đẩy khái niệm xa hơn một chút. Thật vậy, các CCX hiện đang độc lập, được nhóm theo các cặp trong một Tính toán cốt lõi chết (CCD) được kết nối bởi Vải vô cực để một cái chết quản lý DDR và các mục/lối ra được gọi là I/o chết (Iod).

AMD khai thác đầy đủ sự phân tách tăng lên khỏi các chức năng. Thật vậy, CCD được khắc trong 7nm trong khi IOD được khắc trong 14nm.

Dưới đây một bài thuyết trình AMD tóm tắt đoạn văn trong Chiplets của bộ xử lý EPYC.

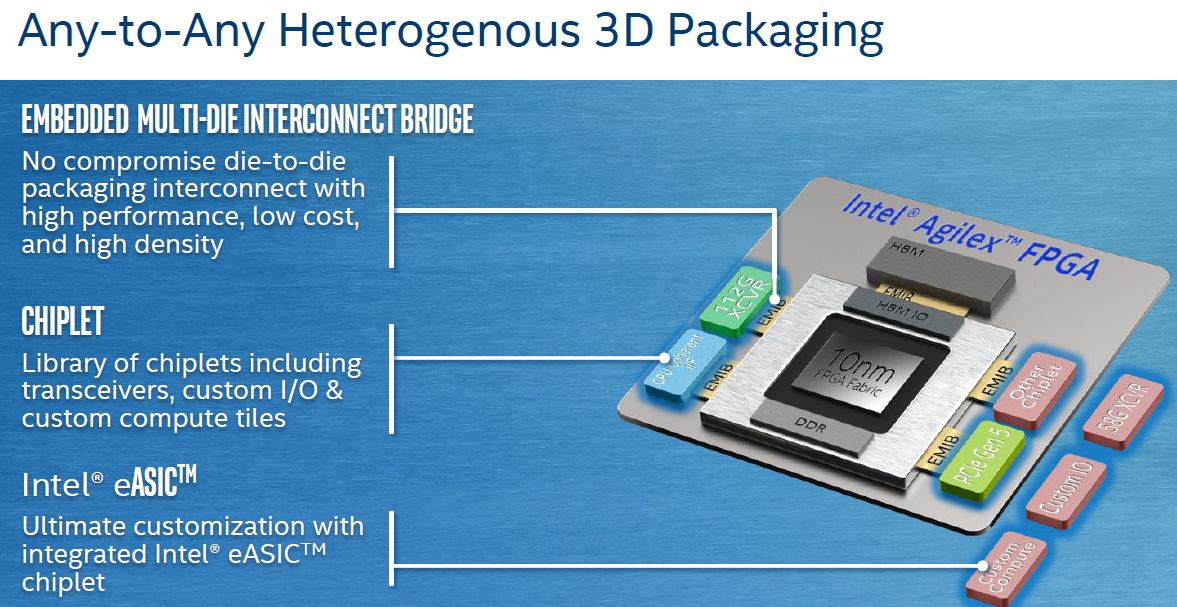

Intel FPGA (Altera)

Bộ xử lý Intel luôn là chip nguyên khối ngoại trừ một vài ngoại lệ như chúng ta có thể thấy khi bắt đầu bài viết này. Tuy nhiên, trong lĩnh vực Intel FPGA (FPGA có thể cấu hình lại) sử dụng chiplets cho thế hệ mới nhất, AgiLex.

Những chiplets này chủ yếu liên quan đến loại transcense được sử dụng (liên kết nhanh) và được gọi Gạch. Nếu Intel cung cấp các phạm vi được xác định trước từ các ô này, thì phải có chip tùy chỉnh cho nhu cầu của riêng bạn.

Các gạch được chia cho tốc độ tối đa của bộ thu phát và các giao thức được hỗ trợ (Ethernet, PCI Express, v.v.): 16g cho P, 28g cho H, 32g cho R, v.v.

Intel cũng gợi lên cho tương lai khả năng kết nối các chiplets tùy chỉnh sẽ cung cấp các chức năng bổ sung. Hiện tại các công ty đã phát hành chiplet ADC/DAC (Jariett Technologies) cũng như một kết nối quang học khác (AYAR Labs).

Cuối cùng chúng ta cũng không được tin rằng các con chip nguyên khối đã chết. Họ luôn có lợi thế, đặc biệt là về giao tiếp nội bộ và độ trễ, điều này có thể rất quan trọng đối với các ứng dụng nhất định yêu cầu chip có kích thước lớn.

Đây là trường hợp của Broadcom và các chip chuyển đổi 400G của nó có sự lựa chọn được giải thích bởi nhà thiết kế trong video này: https: // www.YouTube.Com/xem?V = B-cogmbaug4

Tôi hy vọng bài viết này có nhiều hơn cho bạn và cho phép bạn biết thêm một chút về việc sản xuất chip hiện tại. Tôi đã cố gắng phổ biến một chủ đề phức tạp, tôi cũng hy vọng tôi có thể giữ bạn sau đoạn đầu tiên

Đừng ngần ngại để lại nhận xét nếu một số điểm nhất định vẫn còn khó khăn với bạn, tôi sẽ cố gắng cung cấp chi tiết.

6 bình luận

Câu trả lời này rất hữu ích

Bài viết xuất sắc, cảm ơn bạn @ Zeql !

“Ném tôi vào những con sói và tôi sẽ trả lại gói.” – Seneca

Câu trả lời này rất hữu ích

Tôi đã tự hỏi rằng sự ra đời của các chiplets có thể xem xét một sự tiến hóa nhất định trong phần cứng (cũng như Lớp tiêu dùng cái đó Cấp máy chủ) trong tương lai, hoặc thậm chí là một sự thay đổi mô hình trên con đường mà chúng tôi thiết kế các máy tính cao và tối ưu tổng thể.

Một số hệ thống tích hợp tốt (đặc biệt là tại Apple) không chỉ dựa trên CPU cổ điển rất hiệu quả. Trong một hệ thống giới hạn như một điện thoại thông minh, chúng ta có thể tìm thấy các chip mã hóa H265, các đơn vị tính toán cho AI (Động cơ thần kinh táo) và tất nhiên là đơn vị đồ họa cổ điển.

Do đó, tôi lấy sơ đồ của AMD EPYC của thế hệ thứ 2 và tôi tự hỏi liệu các chiplets có phải là một cách đơn giản để sản xuất khả năng thương mại và công nghiệp từ các đơn vị hoàn chỉnh bắt đầu một số chip chuyên dụng để đạt được hiệu suất tối ưu trong một số nhiệm vụ nhất định. Ví dụ, một đơn vị có thể cung cấp cho các CCD cổ điển, nhưng cũng có DSP, GPU, Transco H265/AV1/VP9/Mạnh, một con chip để làm AES, v.v. và kết nối tất cả thông qua sản xuất IOD/Infinity. Do đó, mỗi nhà sản xuất máy/máy chủ có thể soạn thảo đơn vị cuối cùng sẵn sàng sử dụng bằng cách tự sáng tác và không có chi phí công nghiệp hóa R & D/Faramineurous.

Nó làm tôi nhớ đến khái niệm về APU, nhưng tôi không biết có báo cáo.

Câu trả lời này rất hữu ích

Tôi đã tự hỏi rằng sự ra đời của các chiplets có thể xem xét một sự tiến hóa nhất định trong phần cứng (cũng như Lớp tiêu dùng cái đó Cấp máy chủ) trong tương lai, hoặc thậm chí là một sự thay đổi mô hình trên con đường mà chúng tôi thiết kế các máy tính cao và tối ưu tổng thể.

Một số hệ thống tích hợp tốt (đặc biệt là tại Apple) không chỉ dựa trên CPU cổ điển rất hiệu quả. Trong một hệ thống giới hạn như một điện thoại thông minh, chúng ta có thể tìm thấy các chip mã hóa H265, các đơn vị tính toán cho AI (Động cơ thần kinh táo) và tất nhiên là đơn vị đồ họa cổ điển.

Do đó, tôi lấy sơ đồ của AMD EPYC của thế hệ thứ 2 và tôi tự hỏi liệu các chiplets có phải là một cách đơn giản để sản xuất khả năng thương mại và công nghiệp từ các đơn vị hoàn chỉnh bắt đầu một số chip chuyên dụng để đạt được hiệu suất tối ưu trong một số nhiệm vụ nhất định. Ví dụ, một đơn vị có thể cung cấp cho các CCD cổ điển, nhưng cũng có DSP, GPU, Transco H265/AV1/VP9/Mạnh, một con chip để làm AES, v.v. và kết nối tất cả thông qua sản xuất IOD/Infinity. Do đó, mỗi nhà sản xuất máy/máy chủ có thể soạn thảo đơn vị cuối cùng sẵn sàng sử dụng bằng cách tự sáng tác và không có chi phí công nghiệp hóa R & D/Faramineurous.

Nó làm tôi nhớ đến khái niệm về APU, nhưng tôi không biết có báo cáo.

Vì vậy, bạn nên biết rằng một con chip thường được thực hiện với IP (sở hữu trí tuệ): một chức năng được bán khá sẵn sàng ở cấp độ “bóng bán dẫn” nhưng phải được tích hợp vào thiết kế của nó.

Một ví dụ cổ điển là bộ điều khiển DDR3 trên bộ vi điều khiển trên bảng. Nhà sản xuất vi điều khiển không nhất thiết phải làm chủ DDR3 và không có kỹ năng, thời gian (không mong muốn) để tạo bộ điều khiển DDR3. Do đó, anh ta mua IP từ bộ điều khiển và tích hợp anh ta vào thiết kế của mình.

Bạn phải thành công khi thấy sự khác biệt giữa khả năng IP và Chiplet. Đối với tôi, Chiplet sẽ đến và mang theo một hoặc nhiều tính năng nâng cao và đã vượt qua các bài kiểm tra về bản khắc, do đó, một bước bổ sung trong thiết kế. Nhưng vẫn còn vấn đề kiểm tra toàn bộ đất với tất cả các chiplets. Vì vậy, chúng tôi không thể tạo ra hàng trăm biến thể như Lego. Nó cần tối thiểu thực tế kinh tế.

Nhưng vâng, đối với một tập nhất định, chúng ta có thể tạo ra Ổ cắm carte à la carte.

Ưu điểm lớn là về phía sản xuất của chip: Nếu IP có thể bị từ chối đối với sự tinh tế khác nhau, một con chip để có thể luôn luôn được khắc trong sự tinh tế ban đầu của nó được cải thiện với khắc nhỏ hơn.

Câu trả lời này rất hữu ích

Bên cạnh đó tôi nghĩ rằng các chiplets có thể được sử dụng trong một thiết kế mô -đun. Bạn có một thiết kế với 4 chip, bọ chét có lỗi được phân phối trong suốt quá trình sản xuất và những con có 3 chip hoạt động trên 4 sẽ là một phạm vi bên dưới và rẻ hơn một chút so với những người có 4 công việc.

Giúp đơn giản hóa thiết kế và công nghiệp hóa liên quan đến hoạt động thông thường.

Người yêu phần mềm miễn phí và phân phối Fedora GNU/Linux. #Jesuisarius

Câu trả lời này rất hữu ích

Cảm ơn bạn vì bài viết lớn thú vị này. Tôi sẽ yêu bạn quá nhiều thời gian để chi tiết từng điểm mà bạn không giải thích trong hướng dẫn để thực sự hiểu mọi thứ nhưng dù sao cũng thú vị .

Sử dụng bộ dụng cụ thiết kế Chiplet để giúp mở đường cho tích hợp không đồng nhất IC 3D

Chiplet là một ASIC Die được thiết kế cụ thể và tối ưu hóa cho hoạt động trong một gói kết hợp với các chiplets khác. Tích hợp không đồng nhất (HI) liên quan đến nhiều cái chết hoặc chiplets vào các chipplets hệ thống (SIP). Các thiết bị này được cung cấp để có những lợi ích có thể đồng thuận, bao gồm hiệu suất, năng lượng, khu vực, chi phí và TTM.

Trao đổi thiết kế Chiplet (CDX) bao gồm các nhà cung cấp EDA, Chiplet

Các nhà cung cấp/nhà lắp ráp và bộ tích hợp SIP và là một nhóm làm việc mở để đề xuất các mô hình và quy trình công việc tiêu chuẩn để tạo điều kiện cho hệ sinh thái Chiplet. Hội thảo trực tuyến này tóm tắt các bộ dụng cụ thiết kế chiplet (CDK) cung cấp để giúp chuẩn hóa 2.5d và 3.D thiết kế để tạo ra một hệ sinh thái mở.

Xây dựng một hệ sinh thái để thành công 2.Tích hợp mô hình chiplet 5D và 3D

Tương tự như một quá trình SOC, bạn cần một hệ sinh thái cho Chipplets. Chính cho phép áp dụng thị trường chung và triển khai các thiết kế dựa trên Chiplet bao gồm:

- Công nghệ: 2.5 d Tương ứng và các quy trình lắp ráp và sản xuất chết 3D

- IP: Các mô hình Chiplet được tiêu chuẩn hóa

- Quy trình làm việc: Design Design Dòng chảy và PDK, CDK, DRM & Lắp ráp các quy tắc

- Mô hình kinh doanh: Chiplet Marketplace

Trọng tâm ban đầu của CDX là 2.Các mô hình Chiplet dựa trên 5D với 3D để theo dõi. Tìm hiểu thêm về những nỗ lực này trong hội thảo trên web.

Trao đổi thiết kế Chiplet (CDX) bao gồm các nhà cung cấp EDA, nhà cung cấp/nhà lắp ráp Chiplet và các nhà tích hợp SIP và là một nhóm làm việc mở để đề xuất các mô hình và quy trình công việc tiêu chuẩn để tạo điều kiện cho hệ sinh thái Chiplet. Hội thảo trực tuyến này tóm tắt các bộ dụng cụ thiết kế chiplet (CDK) cung cấp để giúp chuẩn hóa 2.5d và 3.D thiết kế để tạo ra một hệ sinh thái mở.

Xây dựng một hệ sinh thái để thành công 2.Tích hợp mô hình chiplet 5D và 3D

Tương tự như một quá trình SOC, bạn cần một hệ sinh thái cho Chipplets. Chính cho phép áp dụng thị trường chung và triển khai các thiết kế dựa trên Chiplet bao gồm:

- Công nghệ: 2.5 d Tương ứng và các quy trình lắp ráp và sản xuất chết 3D

- IP: Các mô hình Chiplet được tiêu chuẩn hóa

- Quy trình làm việc: Design Design Dòng chảy và PDK, CDK, DRM & Lắp ráp các quy tắc

- Mô hình kinh doanh: Chiplet Marketplace

Trọng tâm ban đầu của CDX là 2.Các mô hình Chiplet dựa trên 5D với 3D để theo dõi. Tìm hiểu thêm về những nỗ lực này trong hội thảo trên web.

Hình ảnh bị rò rỉ cho thấy một thiết kế đầy tham vọng của Chiplet cho GPU AMD Radeon

Hình ảnh bị rò rỉ cho thấy một thiết kế đầy tham vọng của Chiplet cho GPU AMD Radeon

- qua

- Trong tin tức

- Vào ngày 16 tháng 8 năm 2023

Một hình ảnh bị rò rỉ đã nổi lên, cho thấy thiết kế GPU với Radeon Chiplet. Thiết kế có mặt giữa 13 đến 20 chiplets khác nhau trên một GPU duy nhất, làm chứng cho phương pháp AMD đầy tham vọng. Thiết kế Chiplet phức tạp hơn này khác với Navi 31 Silicon hiện đang được sử dụng trong Radeon RX 7900 XTX. Mặc dù lần lặp trước của GPU được coi là thế hệ đầu tiên, nhưng nó không sử dụng thiết kế Chiplet thực như bộ xử lý Ryzen gần đây của AMD. Tuy nhiên, quan niệm của NAVI 4C được tiết lộ đại diện cho một tiến bộ đáng kể, bởi vì nó kết hợp một số chiplets tính toán, cũng như các chiplet I/O khác biệt, trên một chất nền duy nhất. Hình ảnh bị rò rỉ trình bày 13 chiplets, với khả năng chip bộ điều khiển bộ nhớ bổ sung không được hiển thị trên hình ảnh.

Để xác nhận tính xác thực của hình ảnh, bằng sáng chế có liên quan năm 2021 thảo luận về khái niệm mô đun trong các bộ xử lý song song được nêu bật. Các mẫu bằng sáng chế gần giống với thiết kế được hiển thị trong hình ảnh bị rò rỉ, thậm chí cho thấy khả năng nhiều chiplets ở phía bên kia.

Thật không may, thiết kế của GPU được trình bày trong hình ảnh bị rò rỉ đã bị hủy. Điều này đồng ý với các mối quan hệ gần đây cho thấy giọng nói của AMD cho thế hệ GPU tiếp theo sẽ có trên các chip nguyên khối Navi 43 và Navi 44 dành cho công chúng, thay vì trên các thành phần cao. Tuy nhiên, người ta suy đoán rằng AMD chuyển hướng những nỗ lực của mình đến việc phát triển GPU bao gồm một số chiplets tính toán cho phân đoạn cao của phạm vi đồ họa trong tương lai của nó, có khả năng là RDNA 5.

Mặc dù việc thực hiện một số chiplets tính toán cho đồ họa trò chơi phức tạp hơn so với các tính toán CPU truyền thống, quyết định của AMD để vượt qua các trở ngại thiết kế và hoạt động trên một giải pháp tốt hơn cho RDNA 5 được coi là một bước tích cực. AMD sẽ có một kế hoạch cứu hộ, chẳng hạn như một nút mới cho phiên bản cải tiến của Navi 31.